1 来自 Xilinx 的 DDS 编译器内核

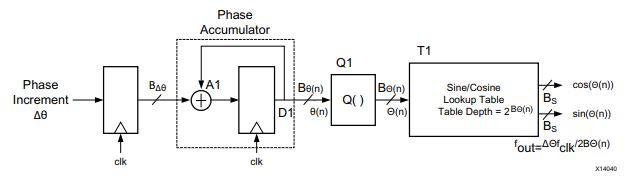

来自 Xilinx 的 DDS 编译器内核的数据表可通过以下链接找到。默认情况下,DDS 编译器的标准模式使用相位截断,下图中可以看到:

组件 D1 和 A1 形成集成器,该积分器计算由查找表 T1 映射到正弦的相斜率。量化器 Q1,用于截合相位角度并生成较低精度的角度表示。此值将馈入查找表的地址端口,该查找表执行从相位空间到时间的映射。

输出频率可以使用以下公式计算:

其中:

- 为DDS所要产生的正弦或余弦信号的频率;

- 为DDS的时钟频率;

- 为相位增量值;

- 为相位位宽,即相位计数器的位数。

当我们需要计算生成一定量赫兹的输出频率所需的相位增量值时,将使用以下公式:

2 基于 System Generator的DDS仿真

来源:CSDN

作者:Signum.Tool

链接:https://blog.csdn.net/wroox111/article/details/104144801